QSD/ISD Switches:

Here is a link the PDF data sheets of analog switches that can be investigated for use in QSD/ISD circuits:

http://www.philcovington.com/HPSDR/QSD_SWITCH/

Interesting ADC:

Here is a link to an interesting ADC by Analog Devices:

http://www.analog.com/UploadedFiles/Data_Sheets/AD7760.pdf

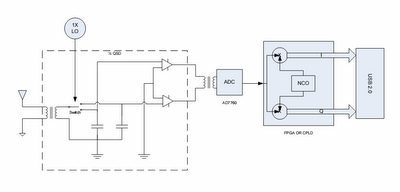

It is a 24 bit, 2.5 MSPS ADC. Here is the circuit idea:

http://www.philcovington.com/HPSDR/TEMP_STUFF/AD7760QSD.pdf

It uses 1/2 of a QSD (not quadrature sampled) to mix the frequency band of interest down to zero Hz with a bandwidth of something like 250 kHz. The IF would be offset to something like 125 kHz. The ADC samples the 1/2QSD output and results in a real data stream. A FPGA or CPLD mixes the real data stream with a complex NCO to generate a quadrature data stream which is sent over USB to the PC where the remaining processing is done. The advantage is a 1 X LO and no I/Q balance problems. One disadvantage is that your sampling rate should be 4 times the desired bandwidth. For narrow band applications this should be no problem because the AD7760 will sample up to 2.5MSPS. A 500 MSPS rate into the PC should allow a bandwidth of almost +/- 125 kHz from the LO frequency.

Nice SDR Enclosure?

Ken N9VV sent me a link to a cool PC case:

http://www.origenae.com/product_x15e.htm

Comments

---------------

It uses 1/2 of a QSD (not quadrature sampled) to mix the frequency band of interest down to zero Hz with a bandwidth of something like 250 kHz.

---------------

From it one could understand that you are really converting to zero Hz, not at an intermediate IF.

Pieter-Tjerk PA3FWM has used the 7760 in an experiment with a I/Q radio, see http://wwwhome.cs.utwente.nl/~ptdeboer/ham/sdr/#jun2006